Filter Chip Sorting Test Integrated Test System Solution

Solution Overview

MVIT Sorting Test Integrated Machine focuses on chip FT testing. While pursuing faster speed and higher accuracy, it also adheres to the principle of providing stable, reliable and efficient services to users with technology as the support and customer as the center.

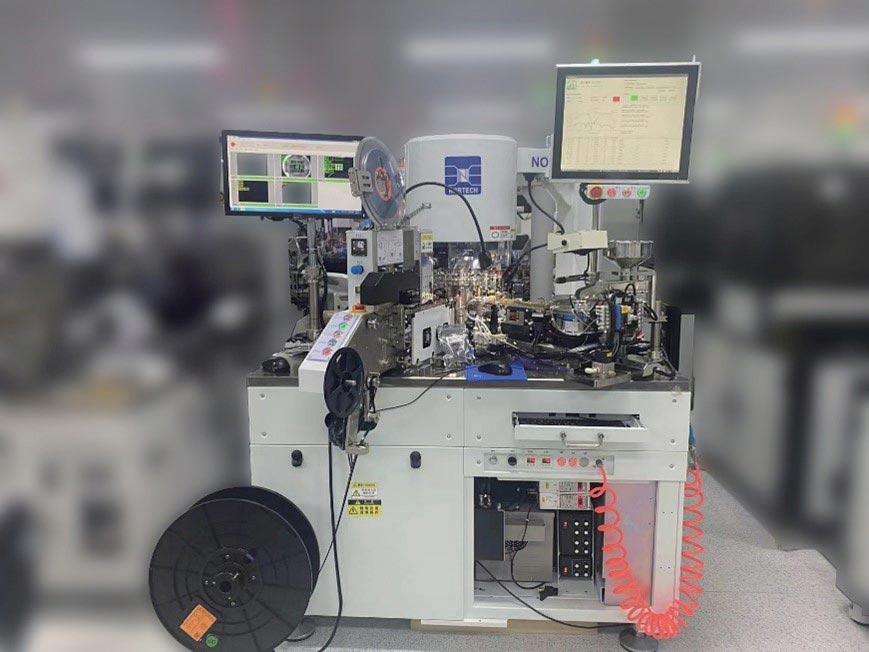

System Configuration

MVIT integrated machine is mainly composed of vector network analyzer, Handler, computer software and related accessories. The system is mainly used for the post-process production of semiconductor chips. It can automatically complete the functions of chip appearance and size detection, electrical parameter testing, laser printing mark, mark detection, classification and screening storage, and final tape and packaging output. With the self-developed computer software, it provides the industry-leading test speed and accuracy.

Feature

- Integrated hardware and software platform

- One-click import of test plan

- Industry-leading UPH

- Real-time data display and export

- Flexible compatibility and scalability

- Quick equipment deployment and factory delivery

- Simple system construction to improve deployment efficiency and cost-effectiveness

Advantage

- Less hardware resources

- Fewer test resource connections

- High-speed IO underlying interaction

- Faster response speed

- Convenient and comprehensive process test chart

Project Based Customized Software

- A brand-new testing interface with flexible definition methods.

- Engineer and operator (OP) operation mode, throughout debugging and production without the need for instrument operation.

- One-click import of product testing plans in (.xml) format to avoid errors.

- Automatically generate network instrument settings status based on Test plan.

- Compatible with typical testing instruments.

- Real-time display of testing curves for easy observation of testing machine status by operators.

- Automatically generate and upload raw test data for each chip.

- Alarm function: Continuous Fail, conductive adhesive replacement, decrease in yield.

Test Plan & Data Output File

- The output header file includes material name, file path, OP information, and test time.

- The formal content includes the number of tests, the specific measured values for each test item of each material, bin information, and the final test results.

- Test Plan introduction: It includes material model, specific parameter settings for VNA, test items for the material, relevant ranges, and BIN results.